Descrizione

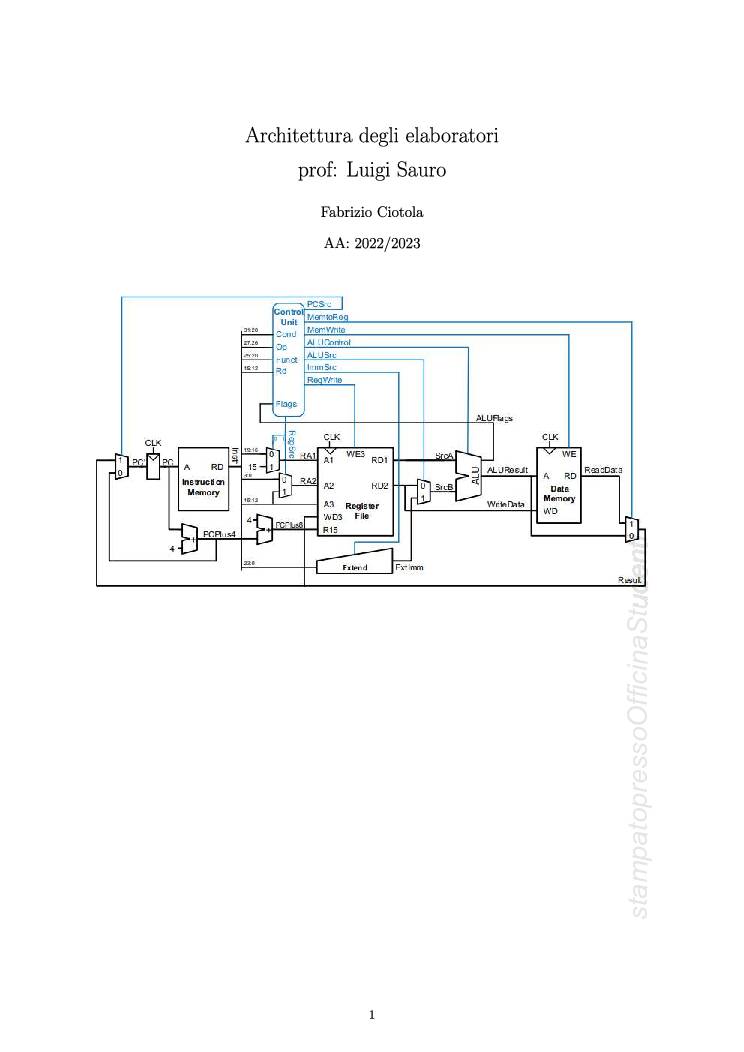

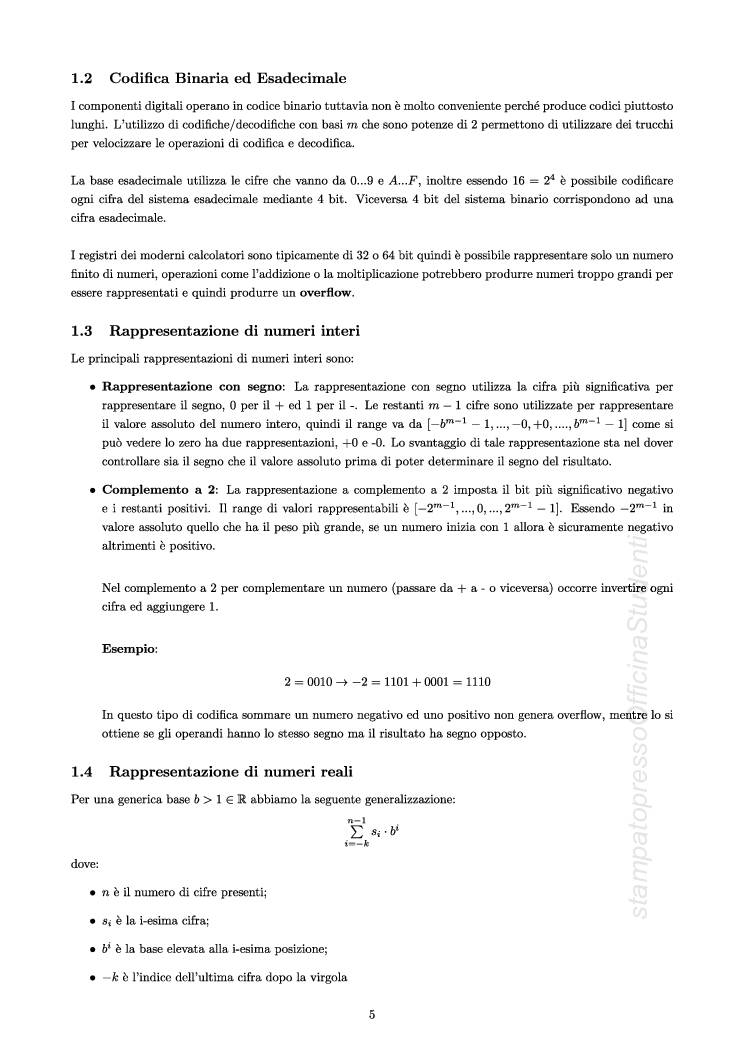

1 Rappresentazione delle informazioni 1.1 Rappresentazione base generica 1.2 Codifica Binaria ed Esadecimale 1.3 Rappresentazione di numeri interi 1.4 Rappresentazione di numeri reali 1.4.1 Rappresentazione in virgola mobile 1.5 UTF-8 2 Algebra di Boole 2.1 Porte logiche 2.2 Funzioni booleane 2.3 Circuiti digitali 2.4 Forma SOP (Sum-of-Products) 2.5 Forma POS (Product-of-Sums) 2.6 Algebra di Boole 2.7 Logica combinatoria su più di due livelli 2.8 Bubble pushing 2.9 Mappe di Karnaugh 2.9.1 Valori don’t care 2.10 Multiplexer 2.10.1 Multiplexer 2:1 2.10.2 Multiplexer 4:1 2.10.3 Sintetizzare le funzioni booleane con i multiplexer 2.11 Decoder 3 Sistemi sequenziali 3.1 Circuiti bistabili, Latch e Flip-flop 3.2 Logiche sequenziali sincrone 3.3 Finite State Machine 3.4 Parallelismo 4 Circuiti aritmetici 4.1 Sommatore 4.1.1 Carry Propagate Adder 4.2 Sottrattore 4.3 Comparatore 4.4 Arithmetic and Logical Unit 4.5 Shifters e Rotators 4.6 Counter 4.7 Shift Register 4.8 Memorie 4.8.1 Tipologie di memoria 4.8.2 Velocit`a tra memorie 5 Architettura 5.1 Linguaggio Assembly 5.2 Principi di un’architettura 5.3 Registri in ARM 5.4 Costanti 5.5 LDR e STR 5.6 Data Processing Instructions 5.6.1 Istruzioni logiche 5.6.2 Istruzioni di shift 5.6.3 Istruzioni di moltiplicazione 5.7 Condition Flags 5.8 Branching 5.9 Memorie 5.10 Chiamate a sottoprogrammi 5.10.1 Chiamate e ritorno a funzione 5.10.2 Parametri di ingresso e valore di ritorno 5.10.3 Registri preservati 5.11 Linguaggio macchina 5.11.1 Data Processing Instructions 5.11.2 Memory Instructions 5.11.3 Branch Instructions 6 Microarchitettura 6.1 Elementi della memoria 6.2 Single-cycle Processor 6.2.1 Datapath 6.2.2 Control Unit 6.2.3 Performance Analysist 6.2.4 Limiti del ciclo singolo 6.3 Multi-cycle Processor 6.3.1 Datapath 6.3.2 Control Unit 6.3.3 Performance Analysist 7 Memorie 7.1 Analisi delle performance di un sistema di memorie 7.2 Cache 7.2.1 Politiche di lettura/scrittura 7.2.2 Come si verifica se un dato è in cache? 7.2.3 Quale dato viene sostituito? 7.2.4 Come ridurre il tasso di miss? 7.2.5 Cache multi-livello 7.3 Memoria virtuale 7.3.1 Traduzione dell’indirizzo 7.3.2 Tabella delle pagine 7.3.3 Translation Lookaside Buffer – TLB

- TEORIA

- INTEGRAZIONE CON LIBRO

- INTEGRAZIONE CON SLIDE

Recensioni

Non ci sono ancora recensioni

Solo gli utenti registrati che hanno acquistato il prodotto possono lasciare una recensione